Московский физико-технический институт (государственный университет) Факультет радиотехники и кибернетики

Кафедра информатики и вычислительной техники

## Магистерская диссертация Разработка модели подсистемы памяти микропроцессора «Эльбрус-2S»

Студент: Куцевол Виталий, группа 718

Научный руководитель: к.т.н. Волконский Владимир Юрьевич

## Формулировка проблемы

«Эльбрус-2S» обладает сложной подсистемой памяти, требующей верификации

- Формальная верификация

- неприменима ввиду сложности системы

- Верификация, основанная на моделировании

- · Моделирование RTL-описания всей системы

- ресурсозатратно

- ограниченный инструментарий отладки

- Использование существующей модели подсистемы памяти, входящей в состав симулятора всей системы на кристалле

- недостаточно детально моделирует тестируемый протокол

- большие накладные расходы

Принято решение создать специализированную модель подсистемы памяти микропроцессора «Эльбрус-2S» - **E2S\_MU**

# Постановка задачи Подсистема памяти микропроцессора «Эльбрус-2S»

#### Ключевые особенности:

- ссNUMA-система

- · распределенная память с неоднородным доступом

- · механизм поддержки когерентности snooping (отслеживание)

- · используется протокол когерентности MOSI

- · размер до 16 процессоров

- Каждый процессор содержит кэши L1 и L2

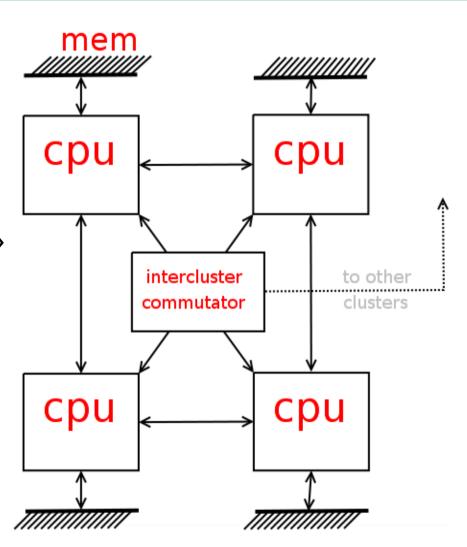

- Для объединения кластеров используется межкластерный коммутатор

# **Постановка задачи Требования к модели**

- Реализация модели подсистемы памяти с поддержкой протокола когерентности

- Реализация интерфейсов для включения в состав тестовой системы

- Гибкость конфигурирования

- Внутренние механизмы самопроверки

- Средства отладки и визуализации

## Модель подсистемы памяти «Эльбрус-2S» Имитационная модель микропроцессора

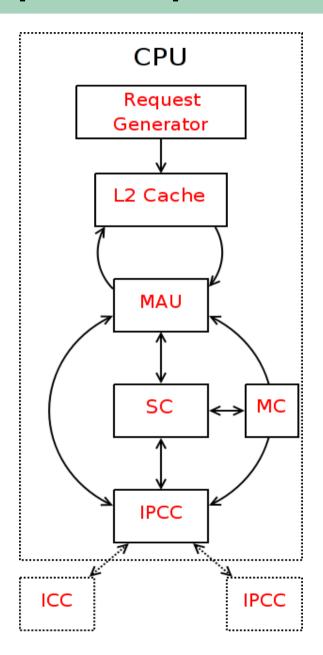

#### Компоненты модели микропроцессора:

- Генератор запросов в оперативную память (Request Generator)

- Кэш второго уровня (L2 Cache)

- Устройство доступа в память (**MAU**)

- Системный коммутатор (SC)

- Контроллер памяти (МС)

## Компоненты, отвечающие за межпроцессорное взаимодействие:

- Контроллер межпроцессорных линков (**IPCC**)

- Межкластерный коммутатор (ІСС)

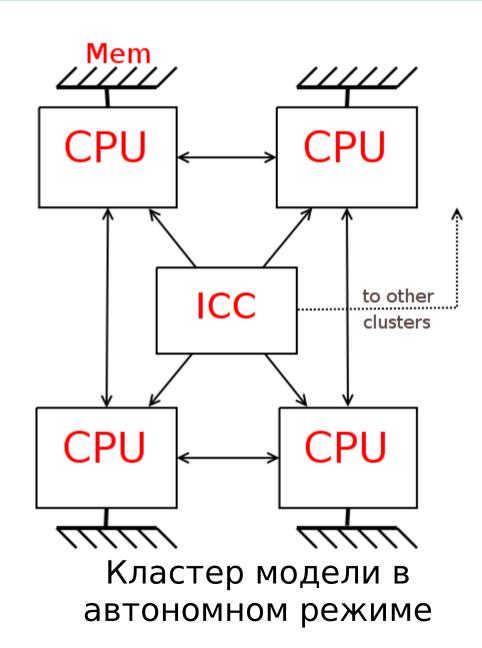

## Модель подсистемы памяти «Эльбрус-2S» Режим автономной работы

В автономном режиме **E2S\_MU** моделирует работу всей системы в любых возможных конфигурациях

#### Назначение режима:

- отладка модели

- проверка корректности используемых тестов

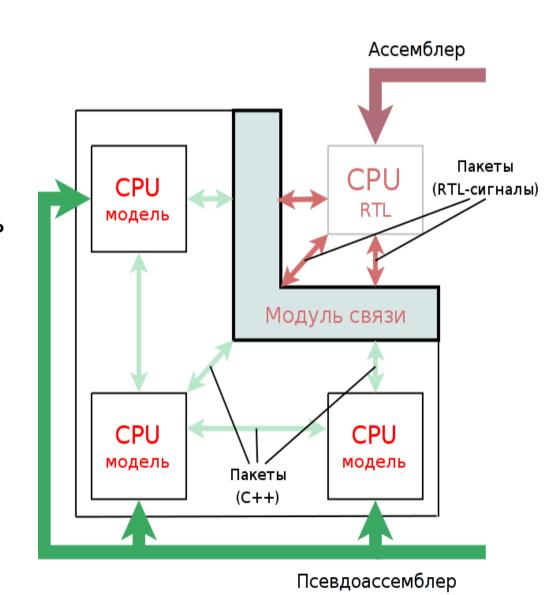

## Модель подсистемы памяти «Эльбрус-2S» Основной режим работы

Основной режим - это работа в составе гибридной тестовой системы

#### Назначение режима:

• отладка RTL-описания подсистемы памяти процессора

#### Тестовая система поддерживает:

- многокластерный режим

- режим «мультилинк»

- режим со включенными справочником

Возможна отладка отдельных составляющих подсистемы памяти:

- системного коммутатора

- межкластерного коммутатора

Базовая конфигурация тестовой системы

## Модель подсистемы памяти «Эльбрус-2S» Интерфейсы с тестовой системой

#### Интерфейсы модели:

- межпроцессорные пакетные интерфейсы

- прием псевдоассемблерных операций обращения в память

Свойства разработанного псевдоассемблера:

- основан на ассемблере «Эльбрус-2S»

- нагляден

- обеспечивает простоту генерации тестов

## Модель подсистемы памяти «Эльбрус-2S» Механизмы самопроверки

- сравнение с эталонной моделью памяти, хранящей допустимые состояния оперативной памяти

- проверка утверждений (assertion)

- проверка корректности входных данных

- проверка допустимости воздействий на компоненты системы

- проверка сохранения инвариантов системы

## Модель подсистемы памяти «Эльбрус-2S» Средства отладки и визуализации

Основное средство отладки — трасса работы симулятора

#### Пример отображения события в трассе

| такт       | устройство  | пакет              | действие    | исходная заявка     |

|------------|-------------|--------------------|-------------|---------------------|

| tick = 587 | cluster#0   | Middle[R64nc]      | try to send | tick = 540          |

|            | cpu#3       | addr = 0x3000b0a00 | to cpu#0    | cluster#0           |

|            | MiddleQueue | nreg = 0x2         |             | cpu#3               |

|            |             | cpu#3              |             | addr = 0x3000b0a00  |

|            |             | rq 0(core0)        |             | test file line #163 |

|            |             | sna = 0            |             |                     |

## Модель подсистемы памяти «Эльбрус-2S» Средства отладки и визуализации

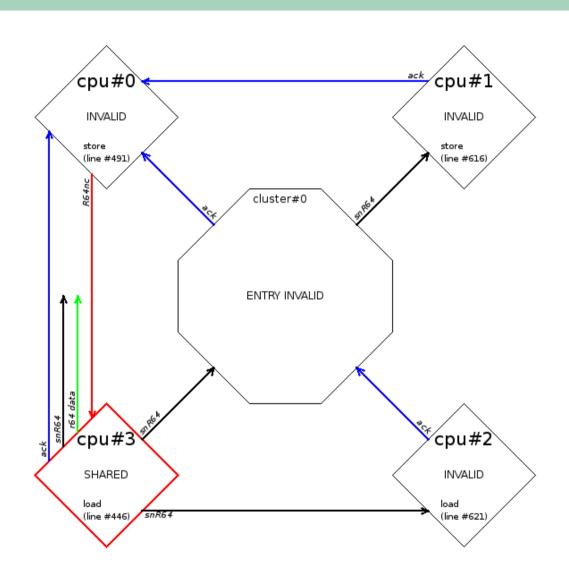

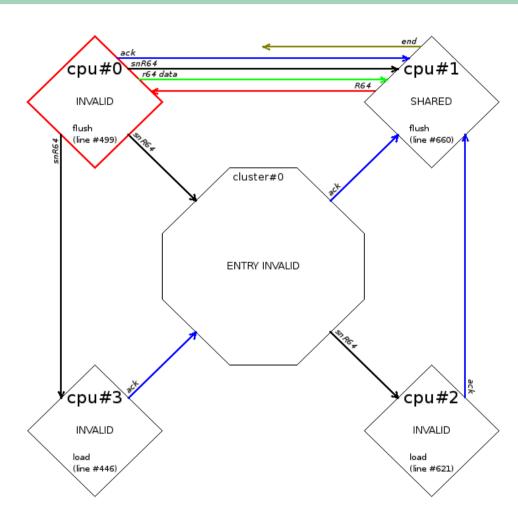

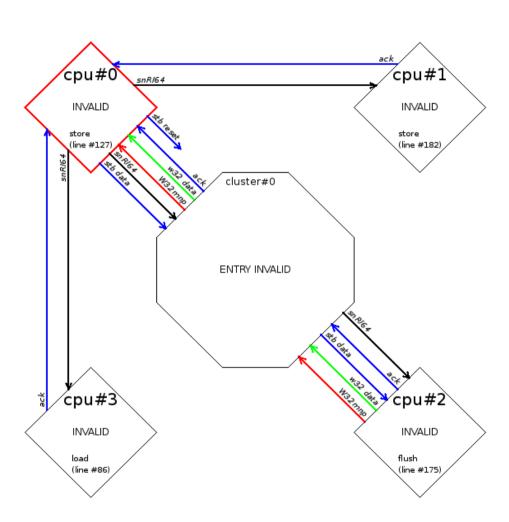

- оконный режим слежения за ходом выполнения запросов по заданным адресам

- отображаются все пакеты относящиеся к выполнению текущих запросов

- отображается идентификатор исполняемого каждым процессором запроса

- отображаются состояния строк L2 кэша

- используется в автономном режиме работы

Выполнение операции чтения

## Результаты

- Разработана и отлажена модель подсистемы памяти микропроцессора «Эльбрус-2S»

- · до 16 процессоров в **ссNUMA** системе

- · протокол **MOSI**

- · механизм snooping

- · средства отладки и визуализации

- гибкость конфигурирования

- · возможность интеграции с RTL

- С помощью тестовой системы, включающей разработанную модель, было найдено 18 ошибок в реализации протокола когерентности на подсистеме памяти микропроцессора «Эльбрус-2S»

- Модель была использована для отладки работы микропроцессора в многокластерном режиме прежде, чем был реализован межкластерный коммутатор

## Спасибо за внимание

## Модель E2S\_MU Функционирование - чтение

1) Requester: дешифрация

псевдоассемблерной команды

2) Requester : L2 формирует первичный

запрос (R64)

3) Requester : MAU сохраняет данные для

приема ответов и передает пакет по линку

4) Home : SC читает данные из памяти

(R64 data)

5) Home: SC рассылает снуп-запросы (snR64)

6) All cpu's : отвечают на снуп-запросы (ack

или ack+data)

7) Requester: принимает ответы,

обрабатывает и завершает операцию (end)

Графический вывод работы модели операция Read

Home — cpu#0, Requester - cpu#1

## Модель E2S\_MU Функционирование - запись

- 1) Requester : дешифрация псевдоассемблерной команды

- 2) Requester : L2 формирует первичный запрос (w32mnp)

- 3) Requester : MAU сохраняет данные для приема ответов и передает пакет по линку

- 4) Home : SC отправляет в Requester запрос за данными (stb\_data)

- 5) Requester: передает данные для записи (w32 data)

- 6) Home : SC рассылает снуп-запросы (snR64) и готовится к приему ответов

- 7) All cpu's : отвечают на снуп-запросы (ack или ack+data)

- 8) Home: принимает ответы, обрабатывает и завершает операцию (stb\_reset)

Графический вывод работы модели операция Write

Home — cpu#0, Requester - cpu#2

## Модель E2S\_MU Псевдоассемеблер

Для генерации входных воздействий разработан псевдоассемблерный протокол обращений в память, предоставляющий возможности:

- простой генераций случайных тестов

- использования трассы работы полной функциональной модели процессора в качестве входного потока для E2S\_MU

- стандартизации воздействий для разнородных составляющих тестовой системы

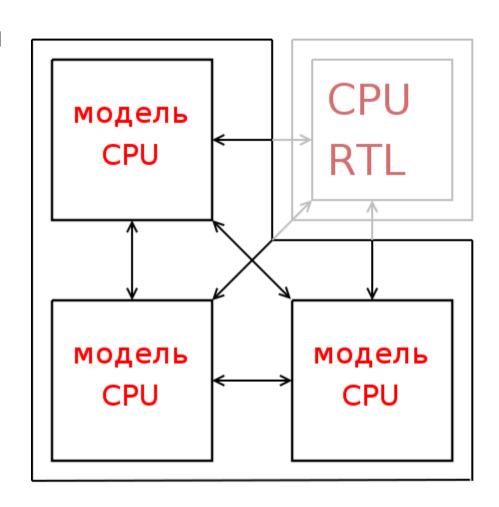

## Модель E2S\_MU Режимы работы

- автономный режим

- отладка модели

- проверка корректности протокола

- проверка корректности используемых тестов

- в одной системе вместе с RTL-моделью процессора

- основный режим работы

- · верификация RTL-описания всей подсистемы памяти процессора

- подстановка вместо составных частей модели соответствующих RTL-описаний

- верификация системного коммутатора

- верификация межкластерного коммутатора

## Результаты

- разработана модель, удовлетворяющая поставленным требованиям

- модель использовалась для верификации RTL-описания процессора

- заложены возможности отладки отдельных составных частей системы

- в процессе верификации с использованием модели был найден ряд ошибок в реализации протокола поддержания когерентности в подсистеме памяти

- модульная структура и стандартные интерфейсы позволяют простую модификацию модели для решения новых задач

### Подсистема памяти микропроцессора «Эльбрус-2S»

- микропроцессор «Эльбрус-2S» имеет три межпроцессорных линка

- кластер содержит до 4-х процессоров

- схема соединения «каждый с каждым»

- гибкая конфигураци системы (многокластерность, режим «мультилинк»)

- для соединения кластеров используется межкластерный коммутатор

Возможная конфигурация кластера