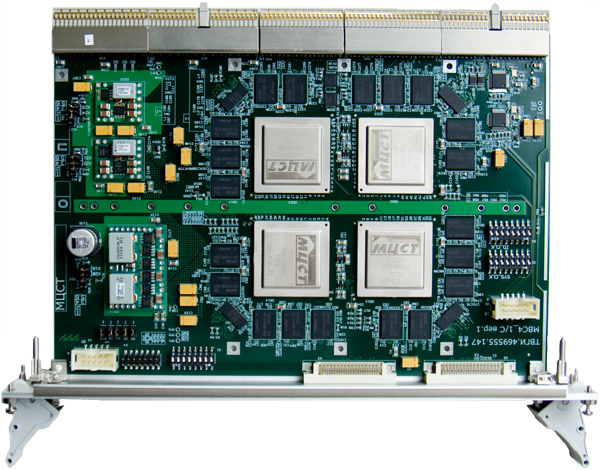

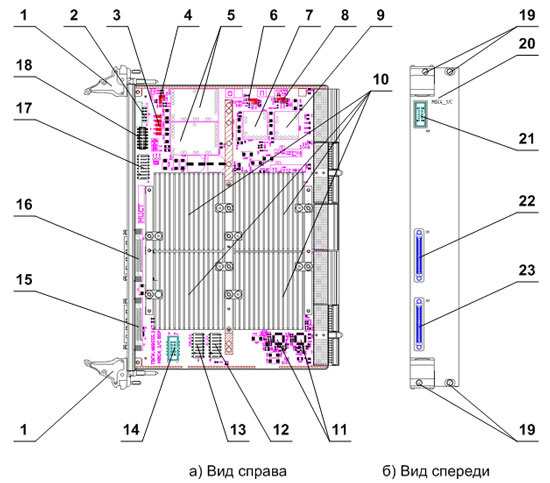

Модуль МВС4_1/C является процессорным модулем и представляет собой модуль в конструктиве «Евромеханика-6U» CompactPCI, устанавливаемый в объединительную панель крейта CompactPCI с помощью стандартных соединителей и занимающую в нем по ширине два слота.

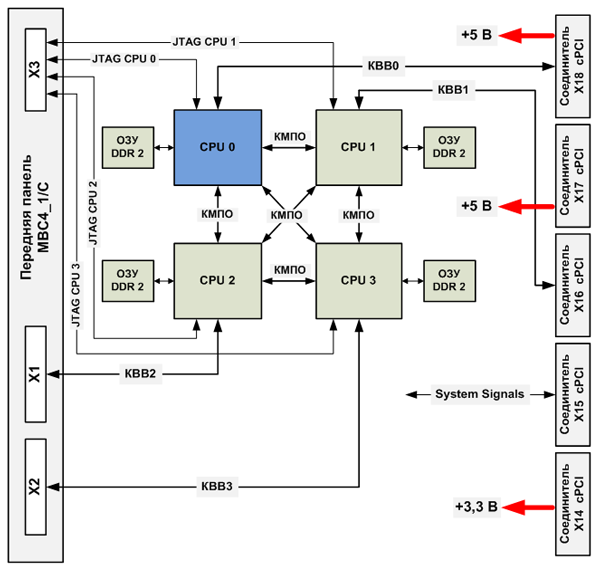

Процессорный модуль МВС4_1/C содержит 4 микропроцессора МЦСТ R1000 (1891ВМ6Я) CPU0–CPU3. Каждая микросхема 1891ВМ6Я в модуле имеет локальную секцию оперативной памяти и может обращаться к секциям оперативной памяти трех других микросхем 1891ВМ6Я непосредственно по каналам межпроцессорного обмена (КМПО).

Кроме 3-х каналов межпроцессорного обмена каждый процессор имеет один некогерентный канал ввода-вывода КВВ. Канал ввода-вывода КВВ0 микросхемы CPU0 используется для связи с системным модулем МВС4_2/C. Каналы ввода-вывода остальных микросхем CPU1–CPU3 могут использоваться как каналы межмашинного обмена в многомашинных системах на базе данного модуля.

Канал КВВ состоит из 10 параллельных дифференциальных полнодуплексных линков. Восемь линков предназначены для данных, один линк управления и один линк для передачи сигнала синхронизации. КВВ может работать в двух основных режимах BUS и DMA:

- BUS-режим предназначен для работы с внешней периферией, например с контроллером ввода-вывода;

- DMA-режим предназначен для межмашинного обмена, например для объединения процессорных модулей в многомашинную конфигурацию.

Пропускная способность (в одну сторону) одного канала КМПО – 2 Гбайт/с, канала КВВ – 1 Гбайт/с.

Процессор CPU0 является выделенным - bootstrap processor. Он отвечает за начальную инициализацию системы.

К каждой микросхеме 1891ВМ6Я подключен 1 канал оперативной памяти ОЗУ DDR2 объемом 1 Гбайт. Суммарный объем оперативной памяти ОЗУ модуля МВС4_1/C – 4 Гбайт, общий для всех микросхем 1891ВМ6Я. Пропускная способность одного канала – 4 Гбайт/с.