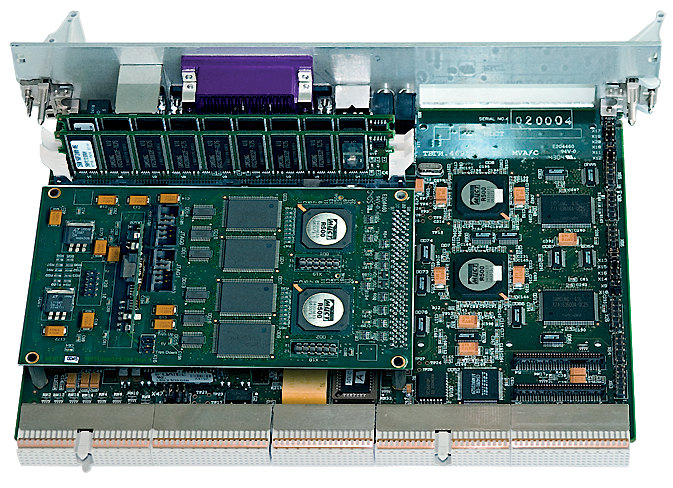

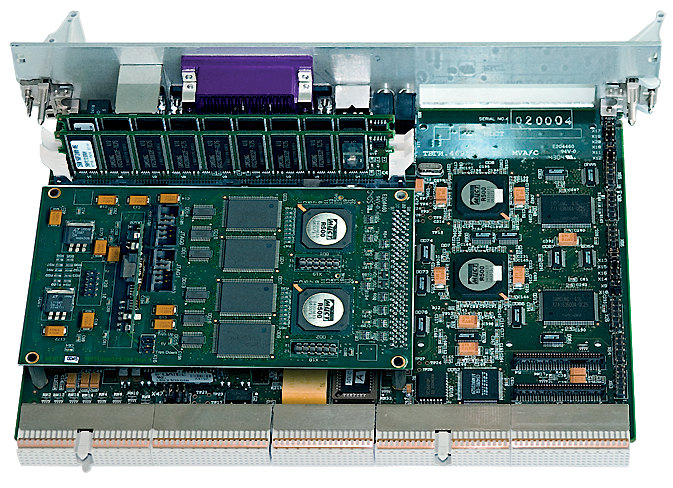

Вычислительный модуль МV/C – высокопроизводительный вычислитель. Представляет собой ячейку в конструктиве cPCI типоразмера 6U. Все внешние соединители модуля расположены на его передней панели.

Вычислительный модуль МV/C – высокопроизводительный вычислитель. Представляет собой ячейку в конструктиве cPCI типоразмера 6U. Все внешние соединители модуля расположены на его передней панели.

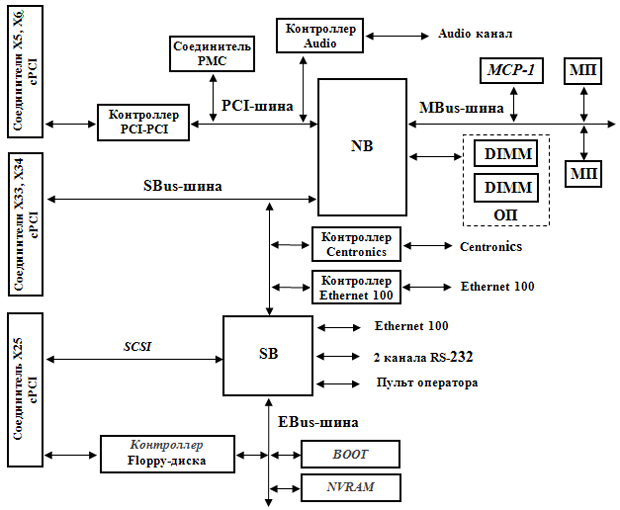

Структура модуля МV/C

Микропроцессор МЦСТ R500 (1891ВМ2) – основной узел модуля. Выполнен на основе архитектуры с сокращённым набором команд – RISC. Отвечает за выполнение арифметических, логических операций и операций управления в машинных кодах. Для обеспечения совместной работы процессоров в модуле МV/С и ячейке МСР-1 используется 64-разрядная высокоскоростная (83,3 МГц) шина MBus. На шине MBus расположен высокочастотный разъём в который устанавливается сменной MBus-ячейка MCP-1. Ячейка MСР-1 бывает однопроцессорной и двухпроцессорной. Таким образом, максимальная конфигурация из 4 микропроцессоров модуля требует наличия одной двухпроцессорной ячейки МСР-1. Кэш-контроллер встроен в микропроцессор, сама кэш-память (2-й уровень) выполнена в виде двух микросхем статической памяти общим объёмом 4 Мбайт (плюс одна микросхема – память тегов 384 Кбайт).

Системный контроллер NB («северный мост») объединяет 4 микропроцессора 1891ВМ2 с оперативной памятью и соединяет шину MBus с периферийными шинами SBusи PCI

Периферийный контроллер SB («южный мост») объединяет в себе:

К периферийной шине EBus подсоединяются:

Шина MBus позволяет объединить до 4 микропроцессоров с оперативной памятью через системный контроллер NB и имеет следующие характеристики:

Оперативная память (ОП) подключается к MBus-шине через системный контроллер NB,обеспечивающий работу с корректирующим кодом (EСC). Контроллервырабатывает управляющие сигналы на накопитель памяти, выдаёт и принимает данные по двунаправленной 72-битовой информационной шине (64 разряда данных и 8 битов корректирующего кода). Накопитель имеет 2 гнезда для 168-выводных сменных модулей памяти. В зависимости от ёмкости и количества микросхем памяти (9 или 18 микросхем ёмкостью 64, 128 или 256 Мбит) ёмкость одного модуля составляет от 64 Мбайт до 512 Мбайт. В накопителе используются синхронные SDRAM DIMM модули с регистрами, работающими в режиме входных усилителей, для управляющих сигналов.

Максимальный объём ОП составляет 1024 Мбайт (1 Гбайт). Схема коррекции позволяет исправлять одиночные ошибки и обнаруживать двойные и блочные (блок – 4 бита) ошибки.

Шина SBus (32-разрядная) используется для подключения контроллеров ввода/вывода. Тактовая частота 25 МГц. Связь двух шин (MBus-SBus) осуществляет системный контроллер NB, содержащий внутренние буфера чтения и записи. Контроллер имеет специальную схему управления памятью для преобразования виртуальных адресов памяти в физические при работе контроллеров ввода/вывода в режиме DVMA. Виртуальный адрес, поступающий от контроллера ввода/вывода по SBus шине, преобразуется в физический адрес памяти на MBus шине.

К SBus шине может быть подключено устройство одного из трёх типов: мастер (master), исполнитель (slave) и контроллер. Мастер – устройство, которое может получить доступ к шине для передачи информации другому устройству. Устройство, которое выбирается мастером в данном цикле обмена, является исполнителем. Контроллер SBus шины представляет собой устройство, которое позволяет другим устройствам, которым необходимо выполнить передачу информации, получить доступ к шине. Эта часть контроллера называется арбитром шины. Вторая функция SBus контроллера – предохранять систему от зависаний. В контроллере имеется таймер, который по истечению 256 тактов обмена выдаёт аварийное прерывание.

Ещё одна функция SBus контроллера – воспринимать сигналы прерываний от абонентов шины, выбирать их по приоритету, шифровать и выдавать в процессор. Таким образом, контроллер SBus шины состоит из арбитра, таймера и шифратора.

Все сигналы SBus шины можно разделить на 6 групп:

Шина сPCI предназначена для подключения внешних устройств, совместимых со спецификацией локальной шины PCI, и подключена к системной шине MBus через хост-мост MBus-PCI, расположенный в системном контроллере NB.

Ширина шины по данным 32 бита, рабочая частота 33 МГц. Соответствует спецификации локальной шины PCI (PCI Local Bus Specification) версии 2.1.

На PCI-шине возможно подключение до восьми ведущих (master) устройств. Реализован равнодоступный (одинаковые приоритеты) алгоритм арбитража.

| Параметр | Значение |

|---|---|

| Микропроцессор | 2 × МЦСТ R500 |

| Тактовая частота процессора, МГц | 500 |

| Кэш команд процессора, Кбайт | 16 |

| Кэш данных процессора, Кбайт | 32 |

| Оперативная память, Гбайт | 1 |

| Кэш второго уровня процессора, Мбайт | 4 (внешняя) |

| Каналы ввода/вывода | Fast Ethernet, RS-232, Centronics, Audio |

| Средняя наработка на отказ ВК, ч, не менее | 9000 |

| Группа исполнения | зависит от ВК |

| Потребляемая мощность, Вт | 6 |

| Диапазон рабочих температур внешних условий применения, °С | зависит от ВК |

| Год начала производства | 2010 |

Поддерживается стандартный комплект программного обеспечения для платформы SPARC.